# WD9914 General Purpose Interface Bus (GPIB) Controller

WESTERN DIGITAL

## WD9914 General Purpose Interface Bus (GPIB) Controller

## TABLE OF CONTENTS

|                                      | PAGE |

|--------------------------------------|------|

| Features                             |      |

| Description                          |      |

| Pin Designation                      |      |

| Pin Description                      |      |

| Architecture                         | . 3  |

| Registers                            |      |

| Interrupt Mask and Status Register 0 | . 5  |

| Interrupt Mask and Status Register 1 |      |

| Address Status Register              | . 7  |

| Address Register                     | . 7  |

| Auxiliary Command Register           | . 7  |

| Description of Auxiliary Commands    |      |

| Software Reset (swrst)               | . 8  |

| Release DAC Holdoff (dacr)           | . 9  |

| Release RFD Holdoff (rhdf)           | . 9  |

| Holdoff On All Data (hdfa)           | . 9  |

| Holdoff On End (hdfe)                | . 9  |

| Set New Byte Available False (nbaf)  | . 9  |

| For the byte Available Faise (fibal) | . 9  |

| Force Group Execute Trigger (fget)   |      |

| Return To Local (rtl)                |      |

| Force End Or Identify (feoi)         |      |

| Listen Only (lon)                    |      |

| Talk Only (ton)                      | . 9  |

| Go to Standby (gts)                  | . 9  |

| Take Control Synchronously (tcs)     |      |

| Request Parallel Poll (rpp)          | . 10 |

| Take Control Asynchronously (tca)    |      |

| Send Interface Clear (sic)           | . 10 |

| Send Remote Enable (sre)             | . 10 |

| Request Control (rqc)                |      |

| Release Control (ric)                | . 10 |

| Disable All Interrupts (dai)         | . 10 |

| Pass Through Next Secondary (pts)    | . 10 |

| Set T1 Delay (std1)                  | . 10 |

| Shadow Handshake (shdw)              | . 10 |

| Very Short T1 Delay (vstd1)          | . 10 |

| Request Service Bit 2 (rsv2)         | . 10 |

| Bus Status Register                  | . 11 |

| Serial Poll Register                 | . 11 |

| Command Pass Through Register        |      |

| Parallel Poll Register               |      |

| Data In Register                     |      |

| Data Out Register                    |      |

| Direct Memory Access                 | . 12 |

| Terminal Assignments and Functions   |      |

| Transceiver Connections              |      |

| State Diagram Implementation         | 15   |

| Auxiliary Commands                   | 15   |

| Acceptor Handshake                   |      |

| Source Handshake                     |      |

|                                      |      |

Talker And Listener Functions19Service Request Function21Remote/local Function23Parallel Poll Function24Remotely Configured Parallel Poll24Controller Function25Controller Self Addressing25Passing Control25System Controller25System Controller25System Controller25Package Diagrams34Ordering Information45

#### TABLES

| 1.  | WD9914 Read Register                      | 4  |

|-----|-------------------------------------------|----|

| 2.  | WD9914 Write Registers                    | 5  |

| З.  | Auxiliary Commands                        | 8  |

|     | Software Reset Conditions                 |    |

| 5.  | Auxiliary Command State Diagram Mnemonics | 16 |

| 6.  | Acceptor Handshake Mnemnonics             | 17 |

| 7.  | Acceptor Handshake Message Outputs        | 17 |

| 8.  | Source Handshake Mnemonics                | 18 |

| 9.  | Source Handshake Message Outputs          | 19 |

|     | Talker and Listener Mnemonics             |    |

| 11. | Talker Function Message Outputs           | 21 |

| 12. | Service Request Mnemonics                 | 22 |

| 13. | Service Request Message Outputs           | 23 |

| 14. | Remote/Local Mnemonics                    | 23 |

|     | Parallel Poll Mnemonics                   |    |

| 16. | Parallel Poll Message Outputs             | 25 |

| 17. | Controller Function Mnemonics             | 26 |

| 18. | Controller Function Message Outputs       | 27 |

| 19. | Multiline Interface Messages              | 30 |

#### **FIGURES**

| 1.       | Simplified Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

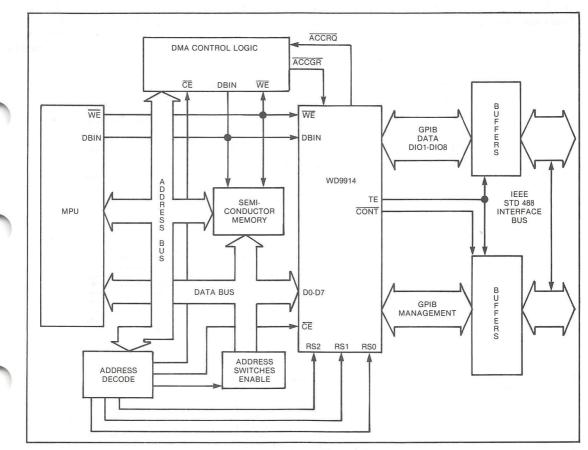

|          | DMA Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13  |

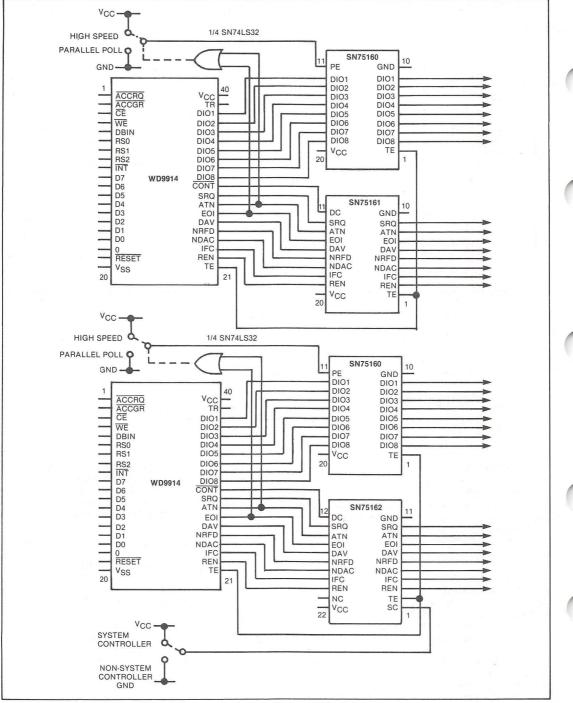

| 3.       | Transceiver Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14  |

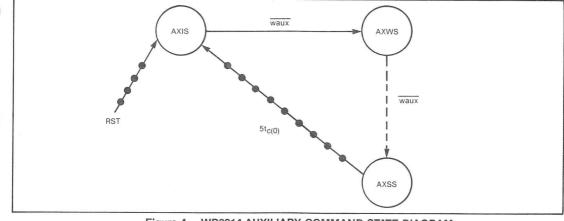

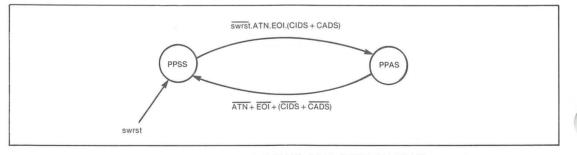

| 4.       | WD9914 Auxiliary Command State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15  |

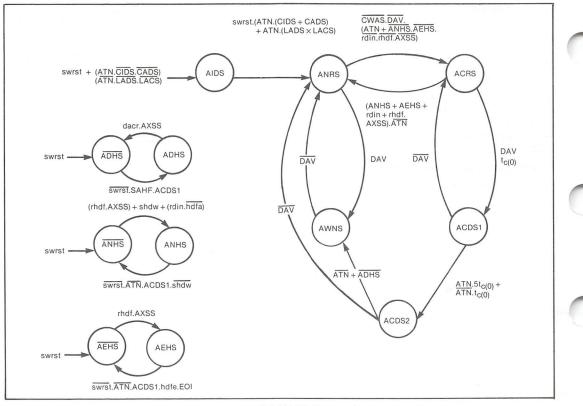

| 5.       | WD9914 Acceptor Handshake State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16  |

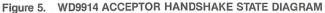

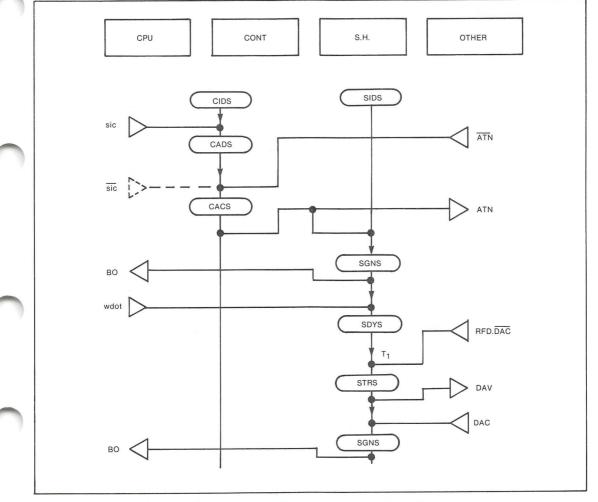

|          | WD9914 Source Handshake State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

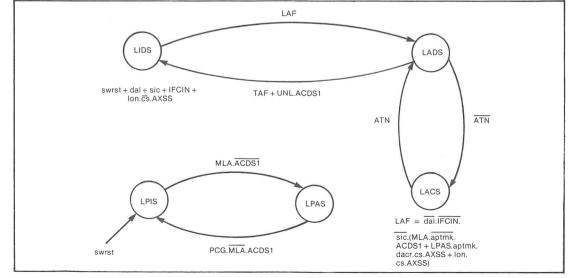

|          | WD9914 Listener State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

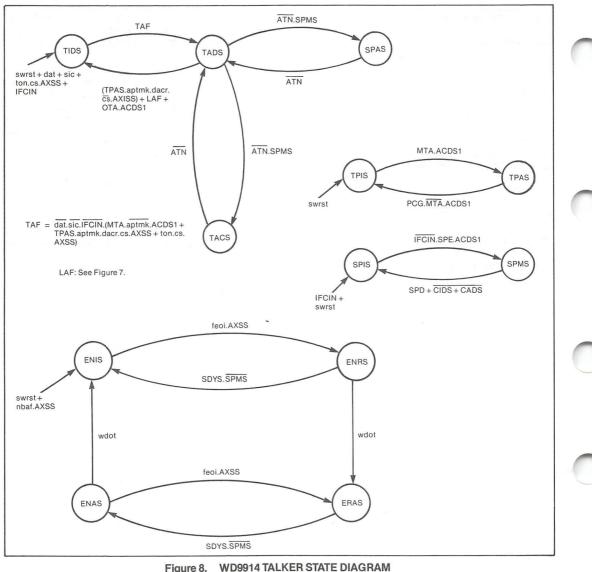

|          | WD9914 Talker State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

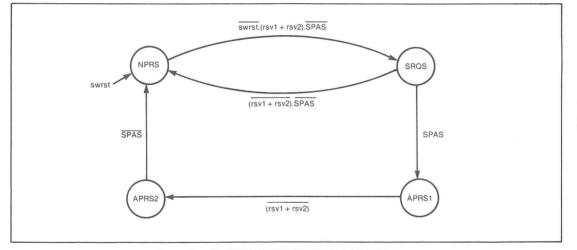

|          | Service Request Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

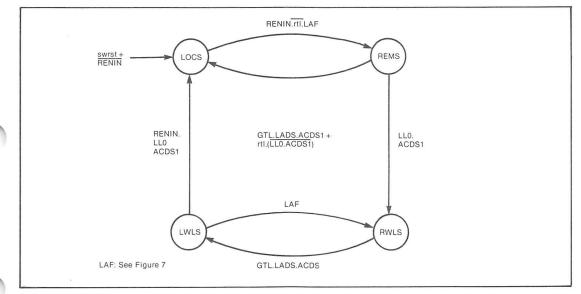

|          | WD9914 Remote Local State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|          | WD9914 Parallel Poll State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

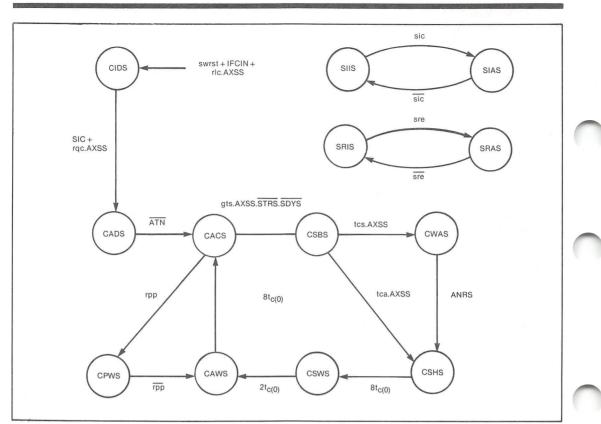

|          | WD9914 Controller State Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

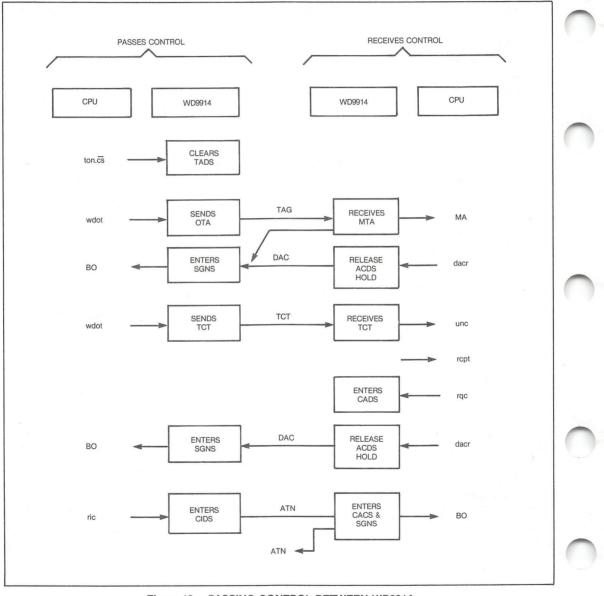

|          | Passing Control Between WD9914                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

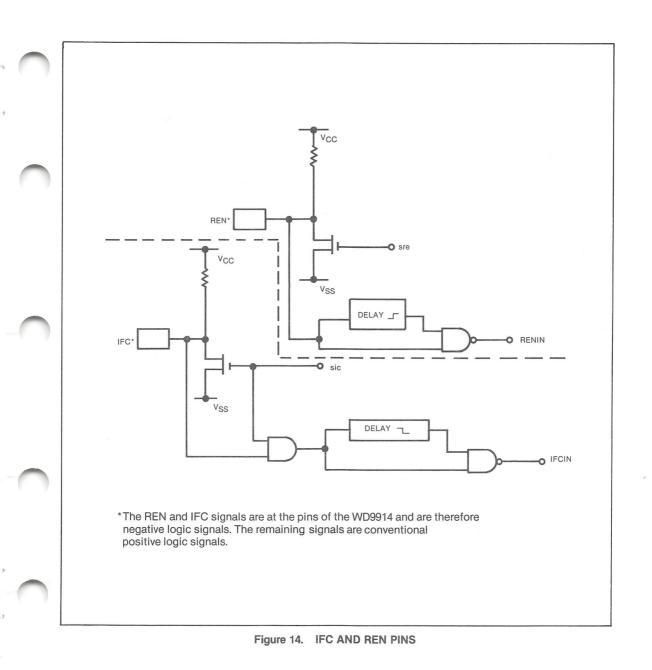

|          | IFC and REN Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|          | Controller Taking Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

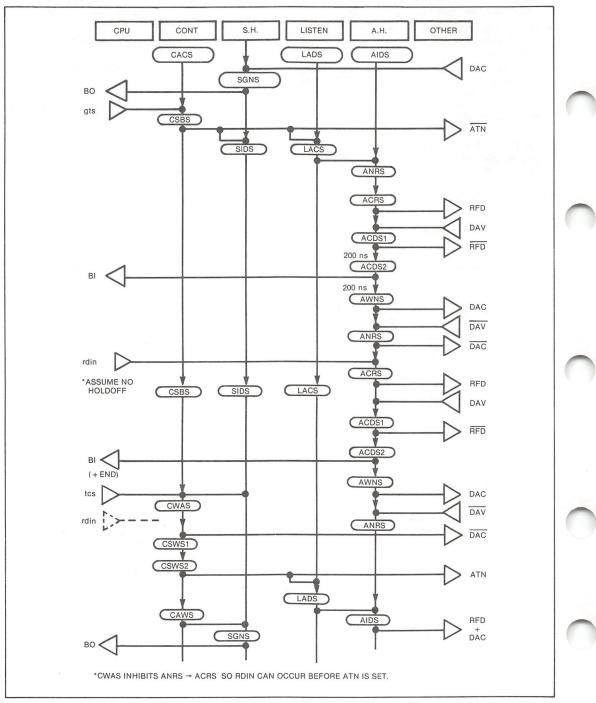

| 16       | Controller as a Listener (Going to Standby)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32  |

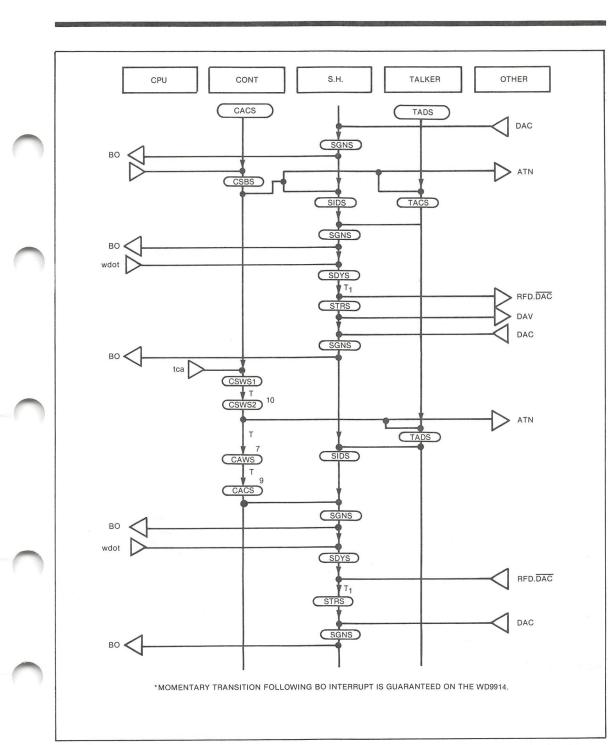

|          | Controller as a Talker (Going to Standby)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

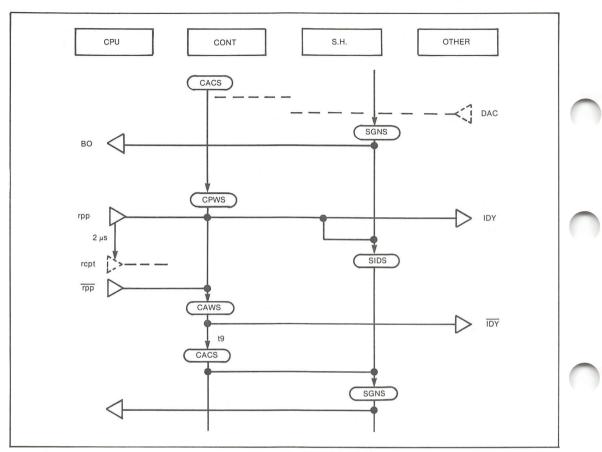

| 18       | Controller Parallel Polling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34  |

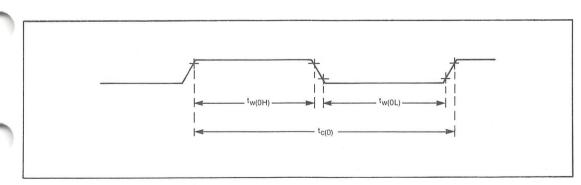

|          | WD9914 Clock Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

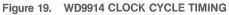

|          | WD9914 Read Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

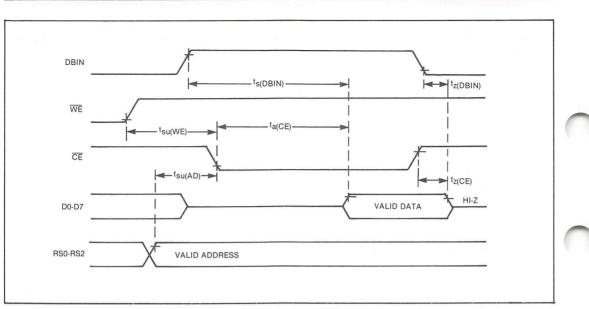

|          | WD9914 Write Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

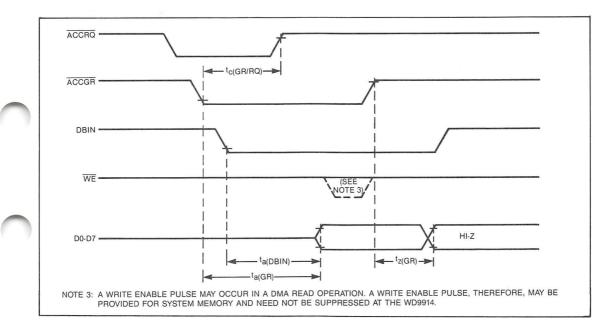

|          | WD9914 DMA Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

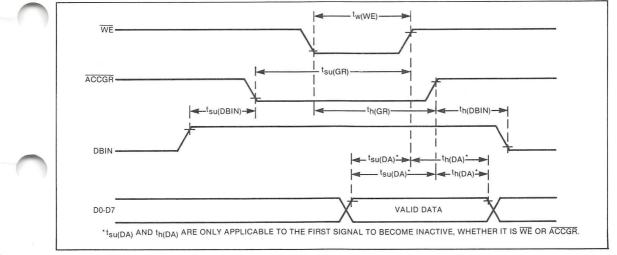

|          | WD9914 DMA Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

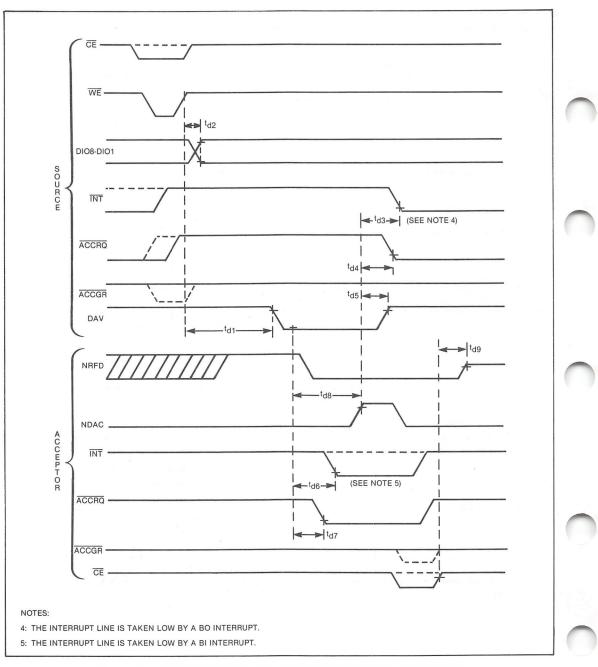

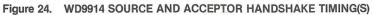

|          | WD9914 Source and Acceptor Handshake Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|          | WD9914 Acceptor Handshake Timing "ATN" True                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|          | WD9914 Response to "ATN" and "EOI"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

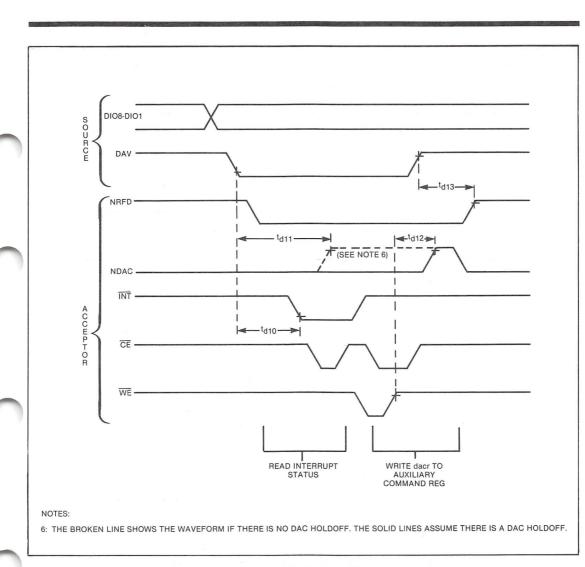

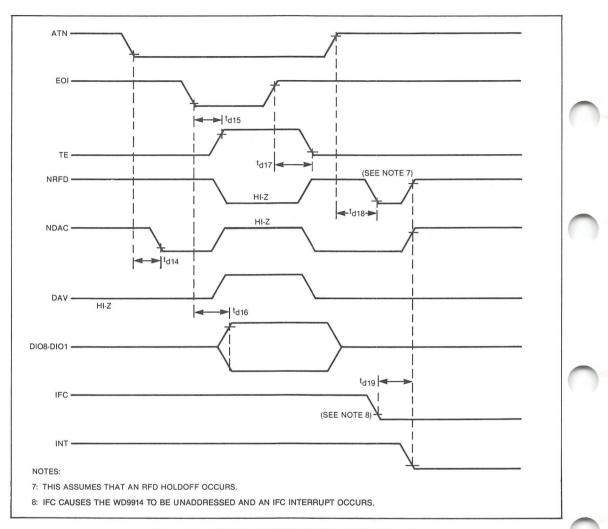

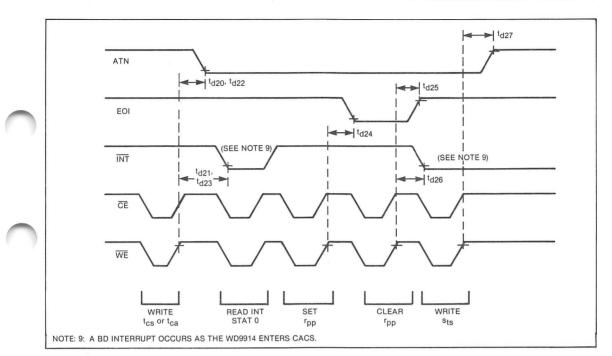

|          | WD9914 Controller Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| time I a | The output of the second | -10 |

#### . . . . . . .

## WD9914 General Purpose Interface Bus (GPIB) Controller

#### FEATURES

- Handles all IEEE-488 1975/78 functions

- Compatible with IEEE-488A 1980 supplement

- Talker and listener function (T, TE, L, LE)

- Automatic source and acceptor handshakes (SH, AH)

- Controller with pass control

- System controller capabilities

- Device trigger and device clear capabilities (DT, DC)

- · Optional automatically cleared 'request service bit'

- Parallel and serial poll facilities (PP)

- Remote/local function with local lockout (RL)

- Single or dual primary addressing

- Secondary address capabilities

- Direct interface to SN75160/161/162 bus transceivers with no additional logic

- Compatible with most microprocessors

- Direct memory access facilities

- Memory-mapped microprocessor interface

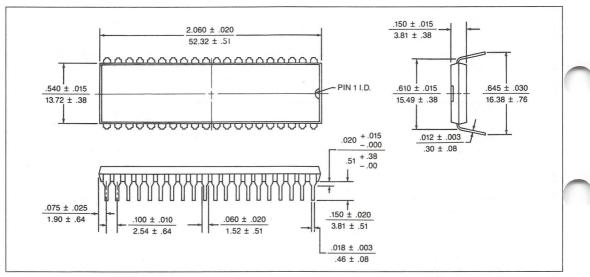

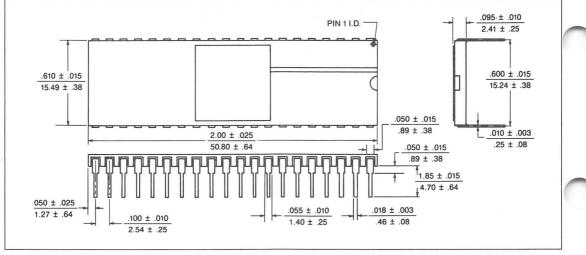

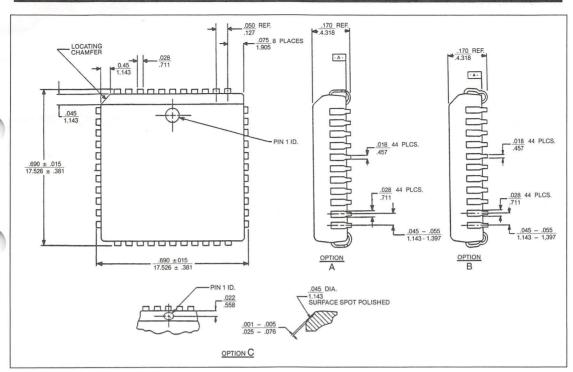

- Available in 40-pin DIP or 44-pin QUAD package

- Single +5V supply

- Compatible with TMS9914A features

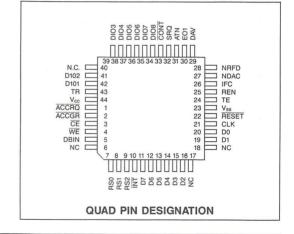

ACCRO 40 □ Vcc ACCGR 2 39 TR DIO1 CE L 3 38 37 WE C 4 DI02 DBIN C 36 DIO3 5 \_\_\_ DIO4 6 RS0 [ 35 RS1 C 7 34 DIO5 DI06 RS2 C 33 8 INT 9 32 31 DIO8 30 CONT 10 D7 C D6 [ 11 SRQ D5 [ 12 29 13 28 D4 F 14 27 EOI D3 C D2 15 26 DAV D1 16 25 NRFD D0 C 17 24 NDAC 23 1FC CLK F 18 RESET 19 22 REN 20 21 TE VSSE **DIP PIN DESIGNATION**

#### DESCRIPTION

The WD9914 provides an interface between a microprocessor system and the General Purpose Interface Bus (GPIB) specified in the IEEE-488 1975/78 standards and the IEEE-488A 1980

supplement. The device is controlled and configured through 8-bit memory mapped registers and enables all aspects of the standards to be implemented, including talker, listener and controller.

## WESTERN DIGITAL

## PIN DESCRIPTION

|             | UMBER<br>QUAD  | SIGNAL NAME       | I/O<br>(TYPE)         | DESCRIPTION                                                                                                                                                                                   |

|-------------|----------------|-------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 1              | ACCRQ             | O(p/p)                | ACCESS REQUEST: This pin becomes active (low) to request a direct memory access.                                                                                                              |

| 2           | 2              | ACCGR             | I                     | ACCESS GRANTED: When received from the direct<br>memory access control logic, this enables<br>the byte onto the data bus. ACCGR must be<br>high when not participating in DMA transfer.       |

| 3           | 3              | CE                | I                     | CHIP ENABLE: $\overrightarrow{CE}$ low allows access of read<br>and write registers. If $\overrightarrow{CE}$ is high, D0-D7 are in<br>high impedance unless $\overrightarrow{ACCGR}$ is low. |

| 4           | 4              | WE                | I                     | WRITE ENABLE: When active (low), indicates to<br>the WD9914 that data are being written to one of<br>its registers.                                                                           |

| 5           | 5              | DBIN              | I                     | DATA BUS IN: An active (high) state indicates to the WD9914 that a read is about to be carried out by the MPU.                                                                                |

| 6<br>7<br>8 | 7<br>8<br>9    | RS0<br>RS1<br>RS2 |                       | REGISTER SELECT LINES: Determine which<br>register is addressed by the MPU during a read<br>or write operation.                                                                               |

| 9           | 10             | INT               | O(o/d)<br>(no pullup) | INTERRUPT: Sent to the MPU to cause a branch to a service routine.                                                                                                                            |

| 10-17       | 11-16<br>19-20 | D7-D0             | I/O(p/p)              | Data transfer lines on the MPU side of the device.                                                                                                                                            |

| 18          | 21             | CLK               | I.                    | CLOCK Input: 500 kHz to 5 MHz. Need not be<br>synchronous to system clock.                                                                                                                    |

| 19          | 22             | RESET*            | 1                     | INITIALIZES the WD9914 at power-on.                                                                                                                                                           |

| 20          | 23             | VSS               |                       | Ground reference voltage.                                                                                                                                                                     |

| 21          | 24             | TE                | O(p/p)                | TALK ENABLE: Controls the direction of the transfer of the line transceivers. Logically, it is: (CACS + TACS + EIO.ATN.(CIDS + CADS). SWRST).                                                 |

| 22          | 25             | REN               | I/O(o/d)              | REMOTE ENABLE: Sent by system controller to<br>select control either from the front panel or<br>from the IEEE bus.                                                                            |

| 23          | 26             | IFC               | I/O(o/d)              | INTERFACE CLEAR: Sent by the system<br>controller to set the interface system into a<br>known quiescent state. The system controller<br>becomes the controller in charge.                     |

| 24          | 27             | NDAC              | l/O(p/p)              | NOT DATA ACCEPTED: handshake line. Accep-<br>tor sets this false (high) when it has latched the<br>data from the I/O lines.                                                                   |

| 25          | 28             | NRFD              | l/O(p/p)              | NOT READY FOR DATA: handshake line. Sent<br>by acceptor to indicate readiness for the next<br>byte.                                                                                           |

| 26          | 29             | DAV               | l/O(p/p)              | DATA VALID: Handshake line controlled by<br>source to show acceptors when valid data is<br>present to the bus.                                                                                |

| 27          | 30             | EOI               | I/O(p/p)              | END OR IDENTIFY: If ATN is false (high), this<br>indicates the end of a message block. If ATN is<br>true (low), the controller is requesting a parallel<br>poll.                              |

#### **PIN DESCRIPTION (Continued)**

| PIN NU<br>DIP                                | JMBER<br>QUAD                                | SIGNAL NAME                                                  | I/O<br>(TYPE)                                                                                | DESCRIPTION                                                                                                                                                         |

|----------------------------------------------|----------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28                                           | 31                                           | ATN                                                          | I/O(p/p)                                                                                     | ATTENTION: Sent by controller in charge. When<br>true (low), interface commands are being sent<br>over the DIO lines. When false (high), these<br>lines carry data. |

| 29                                           | 32                                           | SRQ                                                          | I/O(p/p)                                                                                     | SERVICE REQUEST: Set true (low) by a device to indicate a need for service.                                                                                         |

| 30                                           | 33                                           | CONT                                                         | O(p/p)                                                                                       | Indicates if a device is controller in charge. It is<br>used to control direction of SRQ and ATN in<br>pass control systems. Logically, it is (CIDS +<br>CADS).     |

| 31<br>32<br>33<br>34<br>35<br>36<br>37<br>38 | 34<br>35<br>36<br>37<br>38<br>39<br>41<br>42 | DIO8<br>DIO7<br>DIO6<br>DIO5<br>DIO4<br>DIO3<br>DIO2<br>DIO1 | I/O(p/p)<br>I/O(p/p)<br>I/O(p/p)<br>I/O(p/p)<br>I/O(p/p)<br>I/O(p/p)<br>I/O(p/p)<br>I/O(p/p) | DIO8 through DIO1 are the data input/output<br>lines on the GPIB side. These pins connect to<br>the IEEE-488 bus via non-inverting transceivers.                    |

| 39                                           | 43                                           | TR                                                           | O(p/p)                                                                                       | TRIGGER: Activated when the GET command is<br>received over the interface or the fget command<br>is given by the MPU.                                               |

| 40                                           | 44                                           | VCC                                                          |                                                                                              | Supply voltage ( + 5 V nominal).                                                                                                                                    |

(p/p) = push/pull output.

(o/d) = open drain output with internal pull up.

\*The hardware RESET pin has the following effect on the WD9914:

- Serial and Parallel Poll registers cleared.

-All clear/set auxiliary commands cleared except "swrst."

- "swrst" auxiliary command set. This holds the WD9914 in known states.

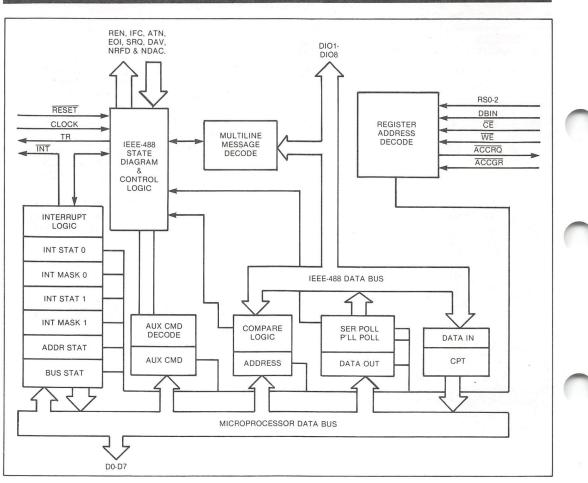

#### ARCHITECTURE

The block diagram of the internal architecture of the WD9914 is given in Figure 1. As previously stated, there are 13 MPU accessible registers of which six are read and seven are write. These registers handle all communication between the IEEE-488 1975/78 bus and microprocessor.

Each register is accessed by putting the relevant address on lines RS0, RS1 and RS2 and performing a memory read ( $\overline{WE} = 1$ , DBIN = 1) or memory write ( $\overline{WE} = 0$ , DBIN = 0) operation. The register addresses and use of each bit is shown in Table 1 for the read registers and Table 2 for the write registers. A full description of each register is given in the following paragraphs.

Implementation of the functions described by the state diagrams of the IEEE-488 standard is carried out in the IEEE-488 state diagram block. Information is received from the IEEE bus and from the internal registers and is combined with the current status of the device (for example, Talker Active State, TACS) to produce the control signals to load registers or handle the handshake or bus management lines.

Figure 1. SIMPLIFIED BLOCK DIAGRAM

| Table 1. | WD9914 | READ | REGISTERS |

|----------|--------|------|-----------|

|          |        |      |           |

| AD          | ADDRESS |     | The second second |      |      |      | BIT ASSI | GNMENT |       |            |      |

|-------------|---------|-----|-------------------|------|------|------|----------|--------|-------|------------|------|

| RS2 RS1 RS0 |         | RS0 | REGISTER NAME     | DO   | D1   | D2   | D3       | D4     | D5    | D6         | D7   |

| 0           | 0       | 0   | Int Status 0      | INTO | INT1 | BI   | BO       | END    | SPAS  | RLC        | MAC  |

| 0           | 0       | 1   | Int Status 1      | GET  | ERR  | UNC  | APT      | DCAS   | MA    | SRQ        | IFC  |

| 0           | 1       | 0   | Address Status    | REM  | LLO  | ATN  | LPAS     | TPAS   | LADS  | TADS       | ulpa |

| 0           | 1       | 1   | <b>Bus Status</b> | ATN  | DAV  | NDAC | NRFD     | EOI    | SRQ   | IFC        | REN  |

| 1           | 0       | 0   | *                 |      |      |      |          |        | 1. 65 | s sala - A |      |

| 1           | 0       | 1   | *                 |      |      |      |          |        | 1.1.1 | 1.1        |      |

| 1           | 1       | 0   | Cmd Pass Thru     | DIO8 | DIO7 | DIO6 | DIO5     | DIO4   | DIO3  | DIO2       | DIO1 |

| 1           | 1       | 1   | Data In           | DIO8 | DIO7 | DIO6 | DIO5     | DIO4   | DIO3  | DIO2       | DIO1 |

\*The WD9914 host interface data lines will remain in the high impedance state when these register locations are addressed. An Address Switch register may therefore be included in the address space of the device at these locations.

#### Table 2. WD9914 WRITE REGISTERS

| A           | ADDRESS |     |               |      |      |      | BIT ASSI | GNMENT |      |      |      |

|-------------|---------|-----|---------------|------|------|------|----------|--------|------|------|------|

| RS2 RS1 RS0 |         | RS0 | REGISTER NAME | D0   | D1   | D2   | D3       | D4     | D5   | D6   | D7   |

| 0           | 0       | 0   | Int Mask 0    |      |      | BI   | BO       | END    | SPAS | RLC  | MAC  |

| 0           | 0       | 1   | Int Mask 1    | GET  | ERR  | UNC  | APT      | DCAS   | MA   | SRQ  | IFC  |

| 0           | 1       | 0   | *             | xx   | xx   | XX   | xx       | xx     | xx   | xx   | xx   |

| 0           | 1       | 1   | Auxiliary Cmd | CS   | XX   | XX   | f4       | f3     | f2   | f1   | fO   |

| 1           | 0       | 0   | Address       | edpa | dal  | dat  | A5       | A4     | A3   | A2   | A1   |

| 1           | 0       | 1   | Serial Poll   | S8 💉 | rsvl | S6   | S5       | S4     | S3   | S2   | S1   |

| 1           | 1       | 0   | Parallel Poll | PP8  | PP7  | PP6  | PP5      | PP4    | PP3  | PP2  | PP1  |

| 1           | 1       | 1   | Data Out      | DIO8 | DIO7 | DIO6 | DIO5     | DIO4   | DIO3 | DIO2 | DIO1 |

\*This address is not decoded by the WD9914. A write to this location will have no effect on the device, as if a write had not occurred.

#### REGISTERS

#### Interrupt Mask and Status Registers 0

The Interrupt Mask and Interrupt Status registers operate independently of each other. The status bits will always be set when the appropriate events occur, regardless of the state of the corresponding mask bit.

All interrupt bits (with the exception of INT0 and INT1, which are not storage bits) are edge triggered and are set when the appropriate condition becomes true. The storage bits are cleared immediately after the corresponding Interrupt Status register is read by the host MPU. If an interrupt condition becomes true during this read operation, then the event is stored. The corresponding bit is set when the read operation ends; hence no interrupts are lost. In addition to being cleared by a read operation, the B0 interrupt is also cleared by writing to the Data Out register, and the BI interrupt is cleared by reading the Data In register.

The interrupt status bits are cleared and held in the O condition while Software Reset ("swrst") is set.

The corresponding bit of the Interrupt Mask register must be set to a 1 if an interrupt status bit is to cause an external interrupt (INT Low) when it is set (i.e., INT = INT STATUS.INT MASK). The mask register is not cleared by "swrst" or the Hardware Reset pin (RESET) and will power on in a random state. It must, therefore, be written to by the host MPU before "swrst" is cleared to avoid extraneous interrupts.

The INTO and INT1 bits of the Interrupt Status register are not true status bits. Int1 will be true if there are any unmasked interrupt status bits set to a 1 in Interrupt Status register 1. INTO will be true if any of bits 2-7 of Interupt Status Register 0 are unmasked and set to a 1. If either INT1 or INTO is true, then the external interrupt pin ( $\overline{INT}$ ) will be pulled low, provided that the Disable All Interrupts feature (dai) has not been set.

The individual bits of Interrupt Status and Interrupt Mask Register 0 are described in the following paragraphs. The conditions which set these bits, shown in parentheses, are given in terms of the state diagrams. Each bit is set on the rising edge of the condition shown.

| xx   | xx   | BI | BO | END | SPAS | RLC | MAC | INT | MASK 0   |

|------|------|----|----|-----|------|-----|-----|-----|----------|

| INTO | INT1 | BI | BO | END | SPAS | RLC | MAC | INT | STATUS 0 |

| D0   | D1   | D2 | D3 | D4  | D5   | D6  | D7  |     | MPU BUS  |

#### **INTERRUPT MASK/STATUS REGISTER 0**

NOTE: A 0 masks and a 1 unmasks the bits in the interrupt mask registers.

- INT1 This will be a 1 when an unmasked status bit in Interrupt Status Register 1 is set to a 1.

- INTO This will be a 1 when any of bits 2-7 of Interrupt Status Register 0 is unmasked and set to a 1.

- BI Byte In. A data byte has been received in the Data In register. If the mask bit is not

set, then no interrupt is generated but a RFD holdoff will still occur before the next data byte is accepted. If the Shadow Handshake feature is used, then this status bit will not be set. This bit is cleared by reading the Data In register as well as after Interrupt Status Register 0 has been read. (Set On: ACDS1.LACS) BO Byte Out. This is set when the Data Out register is available to send a byte over the GPIB. This byte may be either a command if the device is a controller or data if the device is a talker. It is set when the device becomes an active talker or controller, but will not occur if the Data Out register has been loaded with a byte which has not been sent. Subsequently, it will occur after each byte has been sent and the WD9914 returns to SGNS. This bit is cleared by writing to the Data Out register as well as by reading Interrupt Status Register 0. (Set On: SGNS.CACS + SGNS.TASC.SHFS)

#### NOTE:

When a controller addresses itself as a talker and then goes to standby, there will be a momentary transition of the source handshake into SIDS before TACS becomes true and it reenters SGNS. Under these circumstances, the WD9914 is guaranteed to give a BO interrupt on reentering SGNS.

- END This indicates that a byte just received by a listener was the last byte in a string; that is, it was received with the EOI line true. It is set at the same time as the BI interrupt. (Set On: (ACDS1.LACS.EOI)

- SPAS This indicates that the WD9914 has requested service via rsv1 or rsv2 (in the Serial Poll register or Auxiliary Command register) and has been polled in a serial poll. It is set on the false transition of STRS when the serial poll status byte is sent. (Set On: STRS.SPAS.(APRS1 + APRS2)

- RLC Remote/Local Change. This is set by any transition between local and remote states

in the Remote/Local function. (Set On: (LOCS-REMS) + (REMS-LOCS) + (LWLS-RWLS) + (RWLS-LWLS)

MAC My Address Change. This indicates that a command has been received from the GPIB which has resulted in the addressed state of the WD9914 changing. It will not occur if secondary addressing is being used, nor indicate that the WD9914 has been readdressed on its other primary address. (Set On: ACDS1.(MTA.TADSUNT + OTA.TADS + MLA.LADS + UN.LADS)

#### Interrupt Mask and Status Registers 1

The operation of Interrupt Mask and Status Register 1 is similar to that of Interrupt Mask and Status Register 0 except that all bits are true storage bits. The status bits are cleared only following the register being read and by "swrst."

There is one distinct group of interrupts in this register: GET, UNC, APT, DCAS, MA. These are all set in response to commands received over the bus and if unmasked, a Data Accepted (DAC) holdoff will occur when the interrupt in question is set, it may be released with a "dacr" auxiliary command. This is further discussed in the Acceptor Handshake discussions.

The mask bit of the APT Interrupt is further used in the talker and listener functions. When the interrupt is unmasked, the talker and listener functions of the WD9914 implement the extended talker and extended listener functions of IEEE-488. Otherwise these functions implement the talker and listener functions of IEEE-488.

The individual bits of Interrupt Status and Interrupt Mask Register 1 are described below. The conditions which set these bits, shown in parentheses, are given in terms of the state diagrams.

| GET | ERR | UNC | APT | DCAS | MA | SRQ | IFC | INT | MASK 1   |

|-----|-----|-----|-----|------|----|-----|-----|-----|----------|

| GET | ERR | UNC | APT | DCAS | MA | SRQ | IFC | INT | STATUS 1 |

| DO  | D1  | D2  | D3  | D4   | D5 | D6  | D7  | MPU | BUS      |

#### **INTERRUPT MASK/STATUS REGISTER 1**

GET This is set if a Group Execute Trigger command is received. A DAC holdoff occurs if the interrupt is unmasked. The TR pin becomes high when this command is received and persists high for the duration of a DAC holdoff if one occurs. If the interrupt is masked, the TR pin becomes high for approximately five clock cycles. (Set On: GET.LADS.ACDS1)

ERR Error. This is set if the source handshake becomes active and finds that the NDAC and NRFD lines are both high. This indicates that, for whatever reason, there are no acceptors on the bus. (Set On: SERS) UNC

Unrecognized Command. This is set if a command has been received which has no meaning to the WD9914. Unrecognized addressed commands will only cause this interrupt if the device is LADS, except for TCT, which will only interrupt in TADS. Secondary commands will only cause this interrupt if the "pts" auxiliary command has been set previously. A DAC holdoff will occur if this interrupt is unmasked which effectively enables the command pass through feature. Unrecognized commands may be inspected in the Command Pass Through register before this holdoff is released. (Set On: ACDS1. (UCG.LLO. SPE.

SPD.DCL + ACG.GET.GTL.SCD.TCT. LADS + TCT.TADS + SCG.pts)